INTERFACCIA JTAG PER CHIPS A LOGICA

PROGARMMABILE DELLA ALTERA

INTRODUZIONE.

Molto probabilmente chi ha a che fare con l'elettronica analogica o chi usa

microcontroller, conosce appena il significato delle sigle PLD, CPLD, FPGA;

forse già un po' di più la sigla JTAG. E probabilmente assai poco

l'azienda ALTERA, il sui sito Internet è: www.altera.com.

Le prime sigle indicano dei chip a logica programmabile, CPLD=Complex Programmable

Logic Devices, FPGA= Field Programmable Gate Array. Invece JTAG (Joint Test

Action Group, IEEE1149) indica una particoalre interfaccia e il relativo protocollo

per la programmazione e il debug delle logiche programmabili. Altera, invece

è il nome di una delle aziende leader che producono i complessi chip

delle logiche programmabili.

LOGICHE PROGRAMMABILI.

La nascita dei primi circuiti integarti programmabili nasci nei primi Anni Settanta,

quando le schede eelttroniche cominciano a diventare parecchio complesse e utilizzare

solamente i classici circuiti integrati della serie CD40xx e SN74xxx diventa

proibitivo per il grande numero. Così alcune aziende, hanno pensato a

creare dei chip conetenenti un certo numero di porte logiche e una rete di collegamenti

e una seire di connessione programmabili mediante una specie di fusibili. Ed

ecco la nascita delle famose PLA e PAL, che sono leggermente diverse per tipo

struttura. Il difetto principale, oltre al notevo consumo di corrente, era la

programmabilità di una sola volta. Con l'avvento delle memorie EEPROM,

questi chip sono diventati programmabili e cancellalbili elettricamente. Ed

ecco la nascita delle GAL.

Nella figura posta qui sotto è possibile vedere lo schema di un singolo blocco presente in una PAL generica. Si possono vedere le linee elettriche verticali che permettono l'interconnessione tra i vari ingressi ed uscite. Poco più a sinistra si possono vedere prima delle AND cui è poollegata una OR. Le uscite poi possono essere di tipo tri-state, o ad alta impedenza, per poter isolare l'uscita in questione dal resto del circuito esterno.

Con il passare degli anni, il numero di sigle

indicanti dispositivi diversi è aumentato parecchio.

Un'altra evoluzione, circa la programmazione, è stato l'avvento della

tecnologia di programmazione direttamente su scheda, anzichè solamente

su programmatore dedicato. Un buon indizio nella siglatura di questi chip è

la comparsa del prefisso ISP, che significa In-System Programming. Ed ecco che

compaiono alcune sigle tipo ispGAL. Questo tipo di approccio semplifica enormemente

la fase di programmazione ed eventualmente di debug. Questo apre la strada alla

possibilità di cambiare la configurazione del chip anche a prodotto finito.

D'altro canto, la richista sempre maggiore di potenza ha comportato la creazione

di chip sempre più complessi e potenti. E questo non vale solamente per

i microprocessori, e si pensi al famoso Pentium della Intel e i chip analoghi

della concorrenza, ma anche per le loghiche programmabili, che in alcuni casi

contengono più transistors e connessioni esterne (pin) di un processore

dell'ultima generazione di tipo Pentium! Di fatti, alcune FPGA della Altera

o di altre case, dispongono di ben 1500 pin!!!!

E' dal 2000 circa che diversi microcontroller

e microprocessori da 16 o 32 bit dispongono anche del JTAG per la programmazione

e per il debug.

ESEMPIO: il chip EPM7032SLC44-10.

Vediamo le caratteristiche salienti di uno dei chip di semplici della Altera.

Dalla sigla si evince che il chip in questione fa parte della famiglia delle

CPLD MAX I, serie 7000. Il numero di macrocelle è di 32, 2 blocchi di

array logici e il numero di gates è di 600. La "S" che segue

la parte numerica indica il funzionamento a 5Volt, mentre "LC44" indica

che il package è di tipo PLCC a 44 pin, package facilmente utilizzabile

anche a livello amatoriale, hobbistico. Infine, il numero finale, indica la

latenza in ns tra pin a pin.

La memoria di configurazione è basato sulla teconologa EEPROM. Inoltre

il chip è conforme allo standard JTAG per la programmazione.

Per completezza e per ulteriore informazione, qui sotto è riportata la

piedinatura del chip in questione. Si possono notare i diversi pin di alimentazione,

rigorosamente da disaccoppiare con condensatori, e il pin relativi all'interfaccia

JTAG.

PIN |

TYPE |

PIN |

TYPE |

|

1 |

INPUT / GCLRn | 23 |

VCC | |

2 |

INPUT / OE2 / GCLK2 | 24 |

I/O | |

3 |

Vcc | 25 |

I/O | |

4 |

I/O | 26 |

I/O | |

5 |

I/O | 27 |

I/O | |

6 |

I/O | 28 |

I/O | |

7 |

I/O / TDI | 29 |

I/O | |

8 |

I/O | 30 |

GND | |

9 |

I/O | 31 |

I/O | |

10 |

GND | 32 |

I/O /TCK | |

11 |

I/O | 33 |

I/O | |

12 |

I/O | 34 |

I/O | |

13 |

I/O / TMS | 35 |

VCC | |

14 |

I/O | 36 |

I/O | |

15 |

VCC | 37 |

I/O | |

16 |

I/O | 38 |

I/O / TDO | |

17 |

I/O | 39 |

I/O | |

18 |

I/O | 40 |

I/O | |

19 |

I/O | 41 |

I/O | |

20 |

I/O | 42 |

GND | |

21 |

I/O | 43 |

INPUT / GCLK1 | |

22 |

GND | 44 |

INPUT / OE1 |

JTAG.

La sigla JTAG indica un corsorzio tra oltre 200 produttori sia di logiche programmabili,

di microcontroller e anche di apparecchiature di programmazione e di test. Lo

scopo del consorzio era quello di creare uno standard per la programmazione

e il test non solo della logica programmabile o di più logiche programmabili,

ma anche di una parte della scheda elettronica.

Dal punto di vista elettrico le connessioni sono poche, dato che la comunicazione

è di tipo seriale sincrona:

| |

||

| Il flusso dei dati è dal programmatore ai circuiti integrati. | ||

| Il flusso dei dati è dai circuiti integrati al programmatore. | ||

| Il clcock proviene dal programmatore | ||

| Il segnale di selezione di modalità proviene dal programmatore. | ||

| E' un segnale opzionale. la linea di reset proviene dal programmatore. |

Ad ogni cick di clock, un bit viene immesso nel o nei circuiti integrati e un altro bit ne escei. In questo modo, la stringa di bit che compongono il flusso, costituisce il pacchetto di dati relativi alla programmazione e al debug. I dati che vi transitano sono relativi a: configurazione delle celle, identificatore del chip, spazio riservato all'utente, configurazioni particolari, protezione da lettura indesiderata, ed eventualmente altri settaggi specifici del singolo circuito integrato.

Ci sono due particolarità quasi esclusive del JTAG:

DAISY-CHAIN. Con questa

designazione, si intende un particolare collegamento in cui è possibile

programmare e testare più circuiti integrati con una sola connessione.

I collegamenti assengono in questa maniera: in serie per i segnali di

TDI e TDO e in paralleloper i sgenali di TCK, TMS e, se presente, TRST.

Così attraverso le linee di dati transitano un numero di pacchetti

pari a quello dei circuiti integrati da programmare. Questo semplifica

moltissimo la programmazione e il test dell'intera scheda in quando basta

una connessione a 4 fili.

Anche diversi microcontroller che dispongono delll'interfaccia JTAG sono

dotati di questa interessante funzionalità.

La figura posta qui sotto, mostra un esempio di collgamento in daisy-chain.

ccola utility all'interno del PIC in modo che quest'ultimo possa correttamente dialogare con l'ICD2 e fornire tutti i valori di cui il debugger ha bisogno. Con la utility appena citata, ma senza la connessione all'ICD2, il PIC non funziona. Per svincvolarsi dall'ICD2, è necessario caricare il proprio firmware con la funzionalità di programmazione, NON di debugger!

INTERFACCIA JTAG.

E ora finalmente arriviamo a vedere lo schema elettrico.

Innanzitutto lo schema elettrico è quello proposto dalla casa costruttrice

Altera, reso disponibile per l'auto-costruzione. Questo significa che è

uno schema elettrico sicuro e funzionamente e adatto alla programmazione di

qualunque logica programmabile Altera compatibile con lo standard JTAG.

Qui sototo sono riportate le caratteristiche salienti dell'apparecchio proprosto.

| con tutte le logiche programmabili Altera compatibili con lo standard JTAG. | |

| con tutte i software e le varie versioni rilasciate da Altera. | |

solo 5V se si utilizza IC1= SN74HCT244; |

|

| porta parallela di tipo standard. | |

| connettore femmina da 10 poli (2x5). |

Passsiamo ora alla descrizione dello schema elettrico, piuttosto

semplice.

Sostanzialmente l'interfaccia JTAG non è altro che un buffer presente

nel collegamento tra la porta parallela e la connessione JTAG; inoltre vi è

un controllo di abilitazione/disabilitazione delle uscite verso il connettore

JTAG.

Il cuore del circuito è un buffer ottale e driver dotato con l'uscita

di tipo 3-states. Questo tipo di uscita, oltre agli usuali stati logici "0"

e "1", ha il cosiddetto terzo stato, ovvero quello di alta impedenza,

in cui l'uscita è vista come scollegata dal resto del circuito. Le resistenza

presenti in serie alle linee evitano di sovracaricare i driver d'uscita, sia

dell'interfaccia sia della porta parallela in caso di corto circuiti. Invece

le resistenza di pull-up, quelle collegate al positivo, servono per forzare

l'ingresso della porta logica allo stato logico "1".

Qui sotto è riportato lo schema elettrico:

Invece nella tabella posta qui sotto è possibile trovare il valore dei componenti utilizzati nell'apparecchio proposto. Anche in questo caso, il valore indicato è proprio quello consigliato dalla casa costruttrice: quindi si può stare tranquilli!

| R1= 2,2 KOhm R2= 100 Ohm R3= 100 Ohm R4= 100 Ohm R5= 100 Ohm R6= 100 Ohm R7= 2,2 KOhm R8= 100 Ohm R9= 100 Ohm R10= 100 Ohm R11= 100 Ohm R12= 100 Ohm R13= 100 Ohm R14= 2,2 KOhm R15= 2,2 KOhm R16= 100 Ohm R17= 2,2KOhm R18= 100 Ohm R19= 2,2 KOhm |

C1= 100nF multistrato C2= 10uF almeno 16Volt IC1= SN74HC244 Connettore PC: a vaschetta da 25 poli maschio Connettore JTAG: a strip femmina da 10 poli (2x5 poli) |

LA MIA PROPOSTA.

Anche se lo schema elettrico appena visto è abbastanza semplice, può

essere comodo non dover perdere tempo nella costruzione di un prototipo. Così

ho pensato di presentare anche l'apparecchio pronto all'uso, con un circuito

stampato (PCB, Printed Board Circuit) quasi professionale, un idoneo contenitore

contenente sia il PCB sia il connettore a 25 poli per il collegamento al PC

e un cavetto con il connettore JTAG per il collegamento alla scheda da programmare.

Il tutto è abbastanza simile, a livello di aspetto fisico a simili programmatori

professionale venduti da alcune case di circuiti integrati, e mi vengono in

mente i programamtori dei microcontroller MSP430 della Texas Instruments.

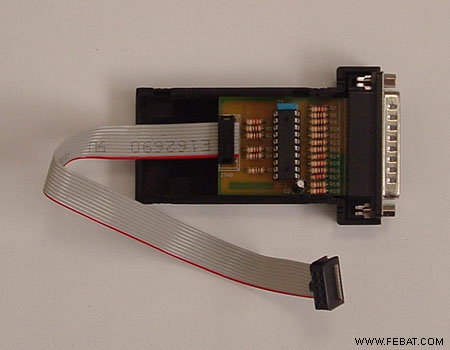

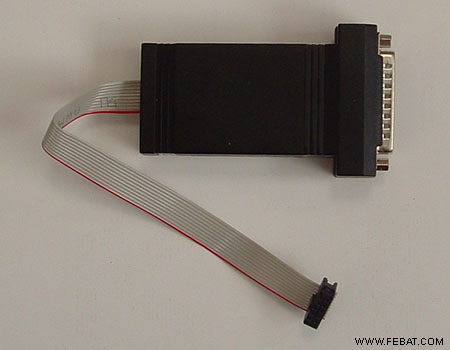

Qui sopra è possibile vedere l'apparecchio aperto. Si possono notare il cavetto con il connettore JTAG, la scheda elettronica con il connettore per l'interfaccia parallela verso il PC. Si noti anche come il cavetto JTAG non sia saldato direttamente su scheda, ma, in caso di danneggiamento, è facilmente sostituibile.

Nella foto soprastante si vede l'apparecchio chiuso, pronto all'uso.Per il collegamento al PC è possibile utilizzare una prolunga per interfacce parallele dotate di un connettore mascio e un connettore femmina, sempre a 25 poli.

NOTA IMPORTANTE.

La scheda proposta è conforme allo standard JTAG ed è equivalente

all'interfaccia MV-Byte-Blaster di Altera: pertanto è compatibile con

tutte le logiche programmabili e con i tools di Altera stessa.

I PREZZI.

Per facilitare il lavoro di professionisti e hobbisti, i due adattatori presentati

sono disponibili anche già montati.

SPESE DI SPEDIZIONE:

Le spese di spedizione €4,00 mediante il servizio

postale di raccomandata e ricevuta di ritorno

PAGAMENTO:

Il pagamento può essere mediante:

Per ogni richiesta, far riferimento al seguente indirizzo e-mail: info@febat.com